作為高速先生的寶藏話題,DDR的設計與仿真一直是我們關注的重點,上周五的文章介紹了DDR的發展歷史、關鍵技術和JEDEC標準,本周繼續對DDR設計及仿真分析的文章進行分類導讀。

01

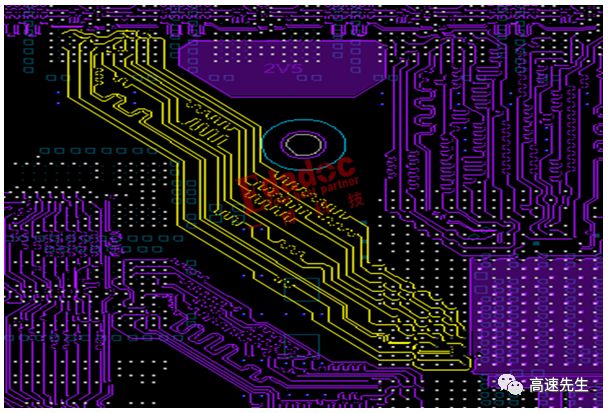

對于Layout工程師而言,最關心的莫過于DDR的設計要點。比如,在布局階段,需要評估DDR走線拓撲對布局的影響(主要針對地址控制類信號)、濾波電容的布局要求、VREF電路布局、匹配電阻的布局等;在布線階段,除了走線拓撲,還需要關注等長要求和電源設計。《DDR3布局的那些事兒》、《DDR3布線的那些事兒》

02

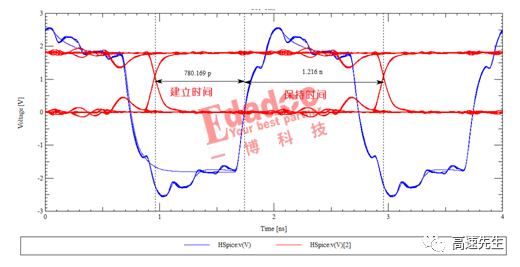

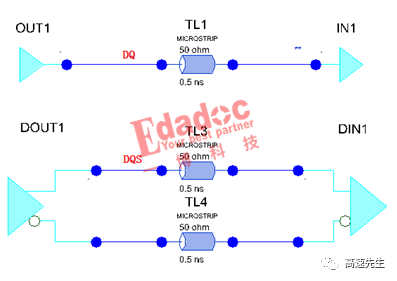

提到DDR設計,少不了線長匹配和時序要求,對于DDR等長要求的總體原則是:地址、控制/命令信號與時鐘做等長。DQ/DM信號與DQS做等長。本文用仿真實例向大家展示DDR中地址相對于時鐘的建立時間與保持時間。《DDR線長匹配與時序(上)》

03

數據信號與DQS又是什么樣的關系呢?DDR和普通的SDRAM相比,讀取速率翻番,這個又該怎么理解?對等長要求的影響如何?《DDR線長匹配與時序(下)》

04

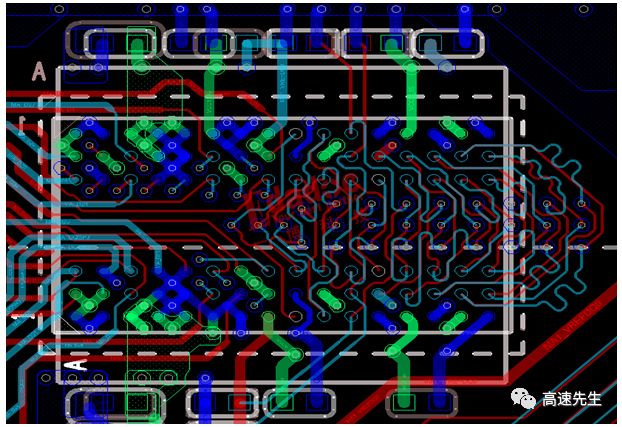

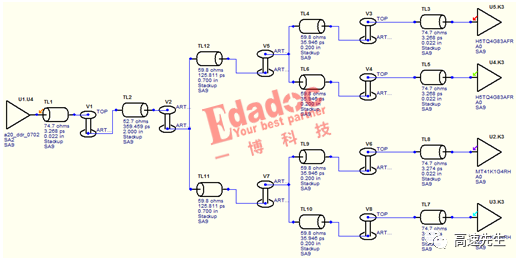

DDR信號網絡多,走線密度大,速率較高,DDR信號質量直接關系到整塊板子的設計成敗,此時,仿真分析會為我們的設計提供有力的支撐。本文通過幾個案例讓初學者對DDR仿真有一個簡單的認識。《DDR信號完整性仿真介紹一》、《DDR信號完整性仿真介紹二》

05

此外,對于DDR這種并行信號的串擾該如何評估?希望這篇文章對你有所啟發。《幾張圖讓你輕松理解DDR的串擾》